Verilog for an FPGA Engineer with Xilinx Vivado Design Suite

Using Xilinx FPGA's

4.53 (1642 reviews)

10 739

students

16.5 hours

content

Jan 2025

last update

$84.99

regular price

What you will learn

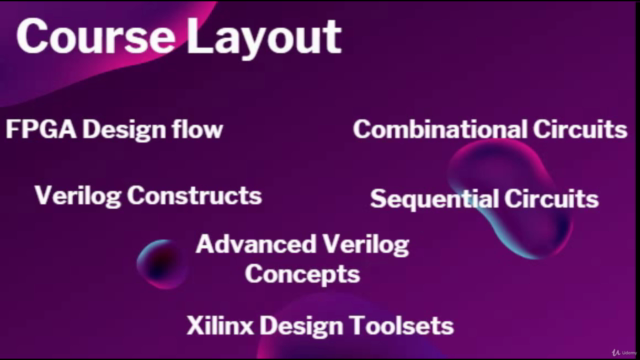

Fundamentals of Verilog Programming that will help to ace RTL Engineer Job Interviews.

Understand Vivado Design Suite flow for Digital System Design.

Hardware Debugging in Vivado viz. Integrated Logic Analyzer, Virtual I/O.

Different Modelling Styles in Hardware Description Language.

How to use Xilinx IP's and create Custom IP's.

IP integrator Design flow of the Vivado.

Writing Verilog Test benches.

Design of some real world projects such as : PMOD DA4 DAC interface, Function Generator, Small Processor Architecture, UART Interface, PWM, BIST for Development boards and many more.

Common Interview Questions

Course Gallery

Loading charts...

Comidoc Review

Our Verdict

Verilog for an FPGA Engineer with Xilinx Vivado Design Suite is an informative course teaching crucial skills for digital system design and RTL engineering. The focus on hands-on exercises and real-world projects set it apart, but some students may struggle due to the instructor's thick accent or grammar issues. The course could improve by incorporating more details about alternative development environments like eda playground while including better translations and expanding coverage of FPGA architectures.

What We Liked

- Comprehensive course covering fundamental Verilog programming and Xilinx Vivado Design Suite for RTL engineers, great for job interviews.

- Practical applications focus with hands-on exercises, real-world projects including DA4 DAC interface, function generator, processor architecture, UART interface, PWM, BIST for development boards.

- Instructive discussion of different modelling styles in hardware description language, Verilog test benches, and Vivado's IP integration design flow.

- Clear instructions on installing tools on your computer, support for using the online environment with compiler and verification

Potential Drawbacks

- Accent of the instructor can sometimes make understanding lectures difficult, possibly requiring slower playback speed or additional focus.

- Limited information shared about eda playground within the course context, no coverage on how to submit assignments involving Vivado.

- Occasional grammar issues and automatic subtitles that may not be accurately translated from the instructor's original words.

- Lack of depth in some sections like FPGA Architecture Fundamentals, specifically variant architectures such as Ultrascale.

Related Topics

2940044

udemy ID

31/03/2020

course created date

10/09/2020

course indexed date

Bot

course submited by